KT88

500+ Head-Fier

- Joined

- Nov 7, 2004

- Posts

- 948

- Likes

- 26

<Edit> As wakibaki has suggested, I'll sum the main few points so it won't get lost in this long post. The goal of the post is to share a design of a simple voltage regulator I've designed, and go over a few of the steps along the way. The final design presented in this post is a simple discrete voltage regulator which includes current limiting (optional) and has just 12uV of output noise (at an output voltage of 24V), which is able to deliver a few amps of current (as long as you keep the pass transistor cool enough). The output noise was measured with tangent's LNMP -> Agilent U1253A, and its BW is 5Hz-100KHz. </Edit>

Over the last few weeks/months I've used most of my spare time to try a design a voltage regulator. This project was mostly for fun and had a few goals. First I wanted to design a voltage regulator of above average performance. Second I wanted to do something different than the zener+differential amplifier combo. Lastly I wanted to go through the entire design process starting from the idea, all the way through the simulations and prototyping, and finally the design of the PCB and final checks.

The initial idea I've had was very simple, about as simple as the zener+BJT follower (which I've called TMVR - Tolis Minimal Voltage regulator ):

):

The idea behind the circuit is very simple, J2 is a CRD (current regulating diode), which can be substituted by a JFET with a constant VGS. M2 is the pass transistor, M3 is the transistor in charge of regulating, and R1-R2 are used to divide the output voltage. The steady-state of the circuit is when J2's current is equal to M3's current in which case M2's gate voltage is constant, and the output voltage is constant. M3 requires a certain VGS (voltage over R2) to pass this amount of current, and since the voltage over R2 is simply a voltage divider from the output the output voltage is known. If for some reason the output voltage changes, M3's VGS will change accordingly, which will change it's current and will regulate the output voltage using M2.

The major disadvantage of this circuit is that its output voltage depends upon M3's VTH (also called VGS(TH)), which has a relatively wide manufacturing spread. However, I've built 4 of these already, and the output voltage has only changed by about 1-2% between them (I've used transistors I've bought several years apart so they should have more than just local mismatches).

I've simulated and checked the design on a proto-board and it works pretty good. The output ripple was similar to the LM317 (up to 100uV - was measured with tangent's LNMP + Agilent U1253A), and the load regulation was similar to the LM317 as well (which is much better than the zener+BJT follower load regulation). However I wanted to try and improve it. I've tried quite a few things including a cascode configuration instead of M3, and replacing J2 with a CCS of higher output impedance (cascode current mirror for example), but there was little gain if any. I've ended up with the following circuit:

This circuit is very much the same as the above circuit, but it has a LPF made by J1-C7-C8. This is used to drive J2. M1 is used in a common gate configuration (regulated by the LPF + D5 which is a zener diode), this forms a cascode connection with M2 which improves line regulation. This circuit has a high dropout voltage of about 5-6V.

I've spent quite a bit of time simulating and playing with the proto-board before I've decided to move to the next level, the PCB. The PCB was designed using FreePCB which is a basic and very easy to use software. I've sent the Gerbers to iteadstudio.com, which is one of the cheapest places you'll find to manufacture a PCB, and hoped for the best.

A few weeks later I've received the package in the mail, inside are the boards:

The only "mistake" I've made is the hole size for C1-C4 and C9 (ceramic caps) which was larger than needed. It works, but its funny to see small ceramic caps in such large holes.

The boards are 5xmX10cm in size (about 2"x4")

Since the circuits above are very similar, they can both be built using this PCB, all you need to do is leave a couple of parts out and place a jumper across M1 and you have the more basic circuit. I've built the "full" circuit and resumed my experiment. There were a few more things I wanted to test. First I wanted to see what affect different transistors at M3's position will have on performance. Second, I wanted to add current limiting to the circuit.

Unfortunately, replacing M3 from IRFU110 to IRFZ24N improved the output noise (under no load with an output voltage of 24V it dropped from 30uV to just 12uV) but has caused the circuit to be unstable with a current of over 500mA or so. I've spent quite a bit of time debugging this, and the cause ended up being the cascode configuration. Shorting M1's drain and source pads has made the circuit stable with no ringing at all even when connecting heavy loads instantly (1.6A). This means there's no longer need for M1, which means I can remove D5 as well. I've replaced J1 with a resistor (its still possible to use a JFET/CRD instead of this resistor if you wish to do so), and ended up with the following circuit:

It's basically the first circuit in this post, but the CCS is connected to a LPF and not directly to the unregulated DC voltage. Once again, this circuit can also be built on the same PCB because its very similar to the previous circuits.

I've measured this circuit as well and was very pleased with the results. Output with no load connected shows a noise of just 12uV (once again measured using the LNMP + U1253A), and with a load of 30ohm (about 800mA) the noise is about 90uV. I've also measured the voltage drop at the output when instantly connecting the load to the regulator. I can only compare to my lab PS which had a drop of 100mV, and this circuit above only had 10mV of drop which means its output impedance is very low at higher frequencies.

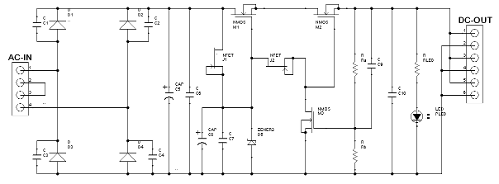

The last thing left for me to do is add current limiting. I didn't want to add the current limiting at the output as this will increase the output impedance. I've added the current limiting the the drain of M2. This has the benefit of not increasing the dropout voltage of the regulator (which is now about 3.5V-4V). The circuit ended up like this (which is the ToliReg v1.0 ):

):

Rsense is 0.55/Imax, Q1 senses the voltage across Rsense, and causes current to flow to R2. R2 turns it back to voltage (with a gain of its resistance value), and this voltage is used to turn on Q2 which in turn takes current away from M2's gate lowering the output voltage. Q3-RLED2-CSLED are used to inform the used the current limiting circut is activated. I didn't put CSLED at Q2's collector because it will limit the voltage at M2's gate to Vce(sat)+VLED which will probably be too high to limit the current in a case of short circuit at the output. The current limiting has beed tested and it works great, which makes me one happy camper

I've redid the PCB so it'll fit this new circuit with the current limiting, and hopefully I'll be able to call this project done. Overall I'm quite happy with the entire process of this project. I've had issues to work out, I've learned how to design a basic PCB, and I have a project I did myself from start to finish which is very satisfying.

BTW, if someone want's to build one and needs the BOM I can organize it and post it. I also have a few boards left if anyone wants one, but they do not include the current limiting (I haven't sent the new boards to be manufactured yet).

Edit2:

Just noticed I haven't updated here for a very long time. So to keep it organized, the final design of the circuit is shown here:

And the black PCB's look pretty good as well:

This is an old picture, I didn't have good resistors for Rsense at the moment, obviously using a metal-oxide is much better. You can also see the LPF I've soldered between Rsense and Q1, this is to slow the current limiting as it had some issue with oscillations once mounted on the PCB (which didn't happen when it was off the board in the proto-typing phase). You can see these parts in the last schematic above as well.

Final noise measurements (Once again, LNMP + U1253A, this time with the IRFZ34N):

24V no load - 6.8uV

24V 800mA load - ~50uV (can be dropped significantly with the use of higher input capacitance)

3.3V no load - 2.6uV

Another member of the forum who has built a few of these measured 4uV with his LNMP with the regulator set to 12V output voltage.

Over the last few weeks/months I've used most of my spare time to try a design a voltage regulator. This project was mostly for fun and had a few goals. First I wanted to design a voltage regulator of above average performance. Second I wanted to do something different than the zener+differential amplifier combo. Lastly I wanted to go through the entire design process starting from the idea, all the way through the simulations and prototyping, and finally the design of the PCB and final checks.

The initial idea I've had was very simple, about as simple as the zener+BJT follower (which I've called TMVR - Tolis Minimal Voltage regulator

):

):The idea behind the circuit is very simple, J2 is a CRD (current regulating diode), which can be substituted by a JFET with a constant VGS. M2 is the pass transistor, M3 is the transistor in charge of regulating, and R1-R2 are used to divide the output voltage. The steady-state of the circuit is when J2's current is equal to M3's current in which case M2's gate voltage is constant, and the output voltage is constant. M3 requires a certain VGS (voltage over R2) to pass this amount of current, and since the voltage over R2 is simply a voltage divider from the output the output voltage is known. If for some reason the output voltage changes, M3's VGS will change accordingly, which will change it's current and will regulate the output voltage using M2.

The major disadvantage of this circuit is that its output voltage depends upon M3's VTH (also called VGS(TH)), which has a relatively wide manufacturing spread. However, I've built 4 of these already, and the output voltage has only changed by about 1-2% between them (I've used transistors I've bought several years apart so they should have more than just local mismatches).

I've simulated and checked the design on a proto-board and it works pretty good. The output ripple was similar to the LM317 (up to 100uV - was measured with tangent's LNMP + Agilent U1253A), and the load regulation was similar to the LM317 as well (which is much better than the zener+BJT follower load regulation). However I wanted to try and improve it. I've tried quite a few things including a cascode configuration instead of M3, and replacing J2 with a CCS of higher output impedance (cascode current mirror for example), but there was little gain if any. I've ended up with the following circuit:

This circuit is very much the same as the above circuit, but it has a LPF made by J1-C7-C8. This is used to drive J2. M1 is used in a common gate configuration (regulated by the LPF + D5 which is a zener diode), this forms a cascode connection with M2 which improves line regulation. This circuit has a high dropout voltage of about 5-6V.

I've spent quite a bit of time simulating and playing with the proto-board before I've decided to move to the next level, the PCB. The PCB was designed using FreePCB which is a basic and very easy to use software. I've sent the Gerbers to iteadstudio.com, which is one of the cheapest places you'll find to manufacture a PCB, and hoped for the best.

A few weeks later I've received the package in the mail, inside are the boards:

The only "mistake" I've made is the hole size for C1-C4 and C9 (ceramic caps) which was larger than needed. It works, but its funny to see small ceramic caps in such large holes.

The boards are 5xmX10cm in size (about 2"x4")

Since the circuits above are very similar, they can both be built using this PCB, all you need to do is leave a couple of parts out and place a jumper across M1 and you have the more basic circuit. I've built the "full" circuit and resumed my experiment. There were a few more things I wanted to test. First I wanted to see what affect different transistors at M3's position will have on performance. Second, I wanted to add current limiting to the circuit.

Unfortunately, replacing M3 from IRFU110 to IRFZ24N improved the output noise (under no load with an output voltage of 24V it dropped from 30uV to just 12uV) but has caused the circuit to be unstable with a current of over 500mA or so. I've spent quite a bit of time debugging this, and the cause ended up being the cascode configuration. Shorting M1's drain and source pads has made the circuit stable with no ringing at all even when connecting heavy loads instantly (1.6A). This means there's no longer need for M1, which means I can remove D5 as well. I've replaced J1 with a resistor (its still possible to use a JFET/CRD instead of this resistor if you wish to do so), and ended up with the following circuit:

It's basically the first circuit in this post, but the CCS is connected to a LPF and not directly to the unregulated DC voltage. Once again, this circuit can also be built on the same PCB because its very similar to the previous circuits.

I've measured this circuit as well and was very pleased with the results. Output with no load connected shows a noise of just 12uV (once again measured using the LNMP + U1253A), and with a load of 30ohm (about 800mA) the noise is about 90uV. I've also measured the voltage drop at the output when instantly connecting the load to the regulator. I can only compare to my lab PS which had a drop of 100mV, and this circuit above only had 10mV of drop which means its output impedance is very low at higher frequencies.

The last thing left for me to do is add current limiting. I didn't want to add the current limiting at the output as this will increase the output impedance. I've added the current limiting the the drain of M2. This has the benefit of not increasing the dropout voltage of the regulator (which is now about 3.5V-4V). The circuit ended up like this (which is the ToliReg v1.0

):

):Rsense is 0.55/Imax, Q1 senses the voltage across Rsense, and causes current to flow to R2. R2 turns it back to voltage (with a gain of its resistance value), and this voltage is used to turn on Q2 which in turn takes current away from M2's gate lowering the output voltage. Q3-RLED2-CSLED are used to inform the used the current limiting circut is activated. I didn't put CSLED at Q2's collector because it will limit the voltage at M2's gate to Vce(sat)+VLED which will probably be too high to limit the current in a case of short circuit at the output. The current limiting has beed tested and it works great, which makes me one happy camper

I've redid the PCB so it'll fit this new circuit with the current limiting, and hopefully I'll be able to call this project done. Overall I'm quite happy with the entire process of this project. I've had issues to work out, I've learned how to design a basic PCB, and I have a project I did myself from start to finish which is very satisfying.

BTW, if someone want's to build one and needs the BOM I can organize it and post it. I also have a few boards left if anyone wants one, but they do not include the current limiting (I haven't sent the new boards to be manufactured yet).

Edit2:

Just noticed I haven't updated here for a very long time. So to keep it organized, the final design of the circuit is shown here:

And the black PCB's look pretty good as well:

This is an old picture, I didn't have good resistors for Rsense at the moment, obviously using a metal-oxide is much better. You can also see the LPF I've soldered between Rsense and Q1, this is to slow the current limiting as it had some issue with oscillations once mounted on the PCB (which didn't happen when it was off the board in the proto-typing phase). You can see these parts in the last schematic above as well.

Final noise measurements (Once again, LNMP + U1253A, this time with the IRFZ34N):

24V no load - 6.8uV

24V 800mA load - ~50uV (can be dropped significantly with the use of higher input capacitance)

3.3V no load - 2.6uV

Another member of the forum who has built a few of these measured 4uV with his LNMP with the regulator set to 12V output voltage.